Quick Specs

Ansys Clock FX automatically identifies and simulates all the clock paths in a design and can account for all critical contributors to clock jitter in each path across multiple processes, voltages, temperature corners and scenarios.

Ansys s'engage à préparer les étudiants d'aujourd'hui à la réussite, en leur fournissant gratuitement un logiciel de simulation.

Ansys s'engage à préparer les étudiants d'aujourd'hui à la réussite, en leur fournissant gratuitement un logiciel de simulation.

Ansys s'engage à préparer les étudiants d'aujourd'hui à la réussite, en leur fournissant gratuitement un logiciel de simulation.

Pour les États-Unis et le Canada

+1 844.462.6797

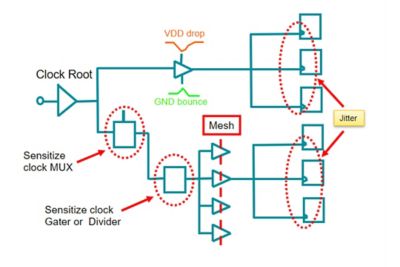

Ansys Clock FX evaluates all the clock paths in an SoC for clock jitter caused by Supply Noise Variation.

Ansys Clock FX allows you to calculate clock jitter with variation on a full SoC, without taking any shortcuts. Its unique cell modeling delivers SPICE accuracy timing for any voltage or variation condition with a single library. Clock FX has a fully threaded and distributed architecture, with the ability to scale to thousands of CPUs.

Ansys Clock FX automatically identifies and simulates all the clock paths in a design and can account for all critical contributors to clock jitter in each path across multiple processes, voltages, temperature corners and scenarios.

Ansys Clock FX is an add-on to existing sign-off flows, with the performance needed to evaluate all clock paths in an SoC for clock jitter on even the largest designs.

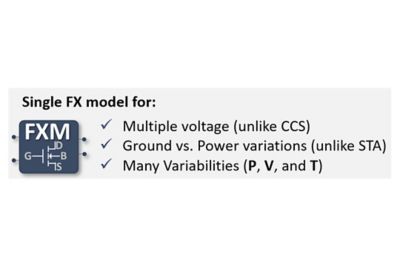

Clock FX’s clock path-based timing for delay and jitter can automatically identify and simulate every clock path in your design. It accounts for all critical contributors to clock jitter across multiple processes, voltages, temperature corners and scenarios. Clock FX leverages SPICE transistor models to create a single library characterization that uses full waveform propagation to provide SPICE accuracy and correctly analyze all variability effects with no shortcuts.

High-capacity SPICE-level timing using unique voltage, temperature and process-variability-aware cell modeling:

Ansys Clock FX mines the dynamic voltage drop on the clock network produced by RedHawk-SC to calculate clock jitter with SPICE-level accuracy. Clock FX accounts for accurate multi-voltage analysis and simulates the delay impact of supply variation on the clock paths.

Ansys Clock FX automatically identifies and simulates all the clock paths in the design using standard cell models or transistor-level SPICE models. Its full waveform propagation provides the accuracy needed to get reliable results at ultralow voltage and advanced processes.

Ansys Clock FX handles transistor level effects such as voltage drop and ground bounce separately. This enables accurate timing at ultralow voltages where margins are razor thin and variability is severe.

Ansys Clock FX leverages the SPICE transistor models and full waveform propagation to provide the accuracy needed to get reliable results at ultra-low voltage for advanced processes. Miller-capacitance and other effects are handled correctly, with no shortcuts.

Ansys Clock FX is threaded and distributed, dramatically reducing turnaround time and memory requirements, compared to Monte Carlo SPICE.

Ansys Clock FX is tightly integrated with the Ansys sign-off power analysis tool RedHawk-SC to obtain the dynamic voltage drop for simulation. It generates a rich set of jitter reports covering various jitter types.

It's vital to Ansys that all users, including those with disabilities, can access our products. As such, we endeavor to follow accessibility requirements based on the US Access Board (Section 508), Web Content Accessibility Guidelines (WCAG), and the current format of the Voluntary Product Accessibility Template (VPAT).